ChatGPT无疑是目前最火,成长最快的一个消费级应用。推出仅仅两个月,月活用户突破1亿。今天小编也想和ChatGPT来聊聊PCIe IP,想看看他知识储备和整理能力怎么样。

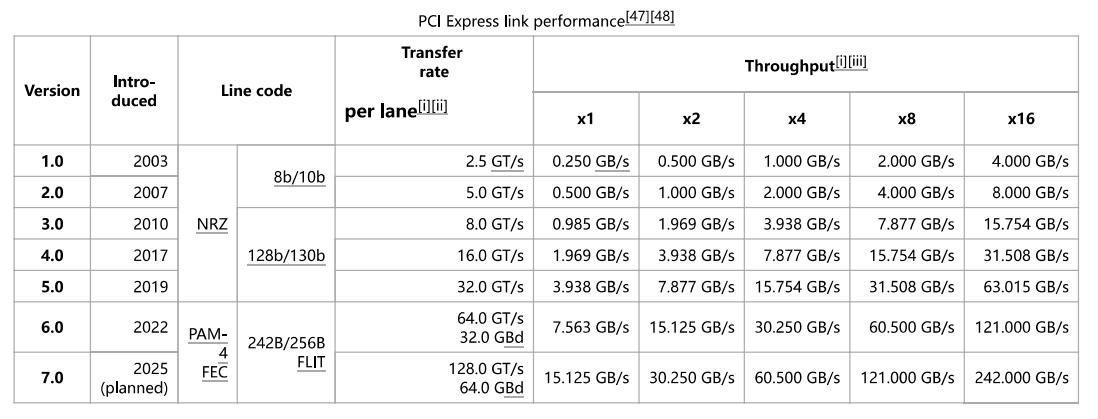

上述两个问题基本没有翻车,PCIe 5.0的理论最大带宽64 GB/s有点不属实,ChatGPT自称学习到最新的数据为2021年的,所以截至到2021年PCI-SIG(发布和维护 PCIe 标准的联盟) 发布的最新版本确为PCIe 5.0,但是其理论单lane单向最大传输速率为32 GT/s,按照128b/130b的编码方式,有效数据吞吐量大约是3.9 GB/s,X16的情况下最大带宽能达到63 GB/s。2022年1月12日,PCI-SIG 组织正式发布了 PCIe 6.0 标准,速度达到了64 GT/s。

应用场景和每代标准比较的问题,比较简单,但是可以看到ChatGPT并没有延用平时常见的版本号、编码方式、传输速率和吞吐量这几个指标来描述,新增了每个时钟周期最多多少位的描述来衡量PCIe的传输能力,这种描述方式小编并没有搜索到类似说法来描述PCIe接口的,但是咨询了工程师们才发现此类描述出现在针对PCIe中PIPE接口规格的设计规则中,可见ChatGPT的数据挖掘的能力属实很强大。

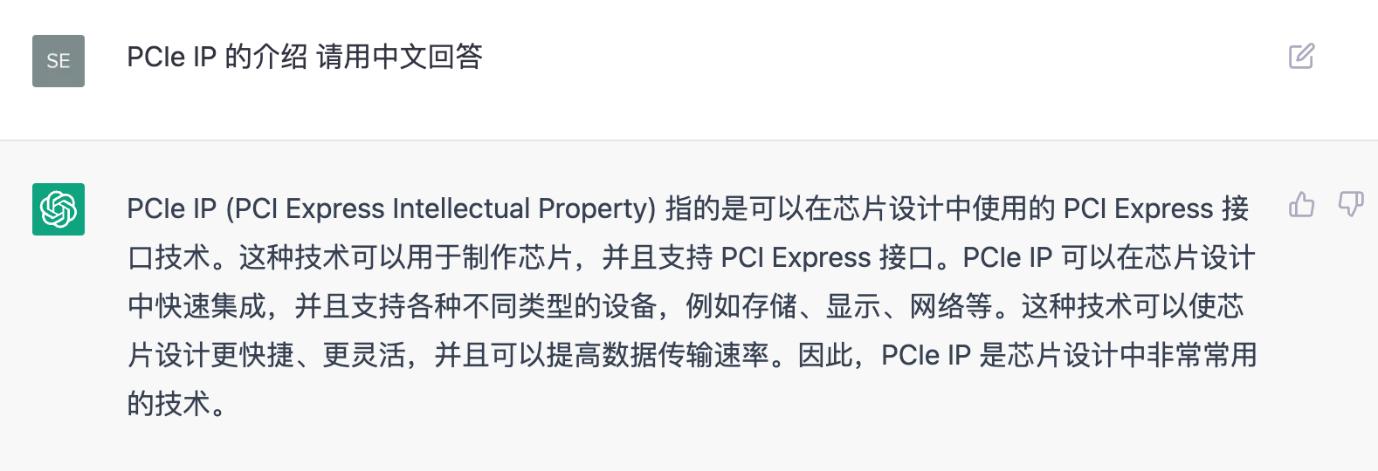

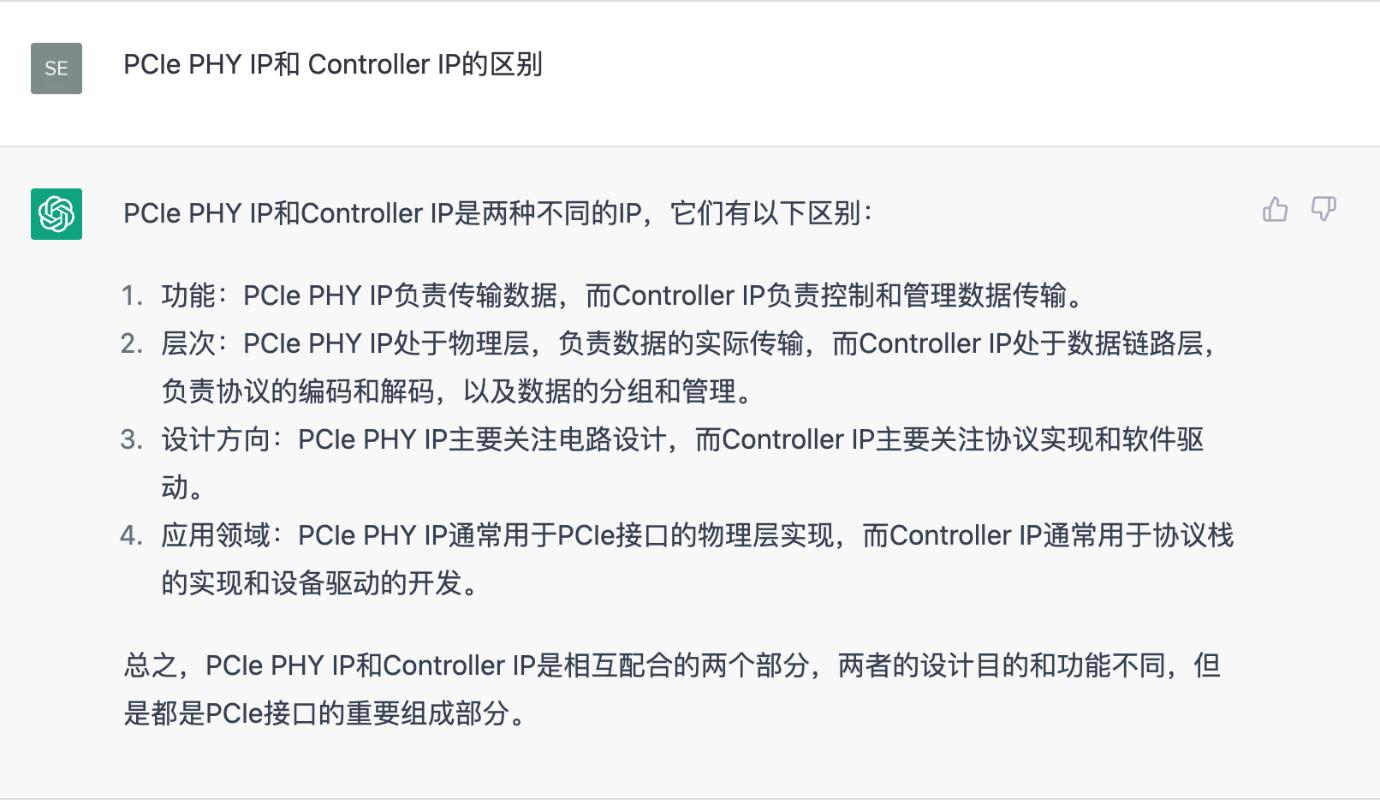

下面进阶到IP问题,对于ChatGPT这类通用AI应用就比较具体了。牵涉到PHY IP的设计,工程师们反应ChatGPT的回答就太粗糙了。

对于小编这种没有此方面深入工程研究的人来说,ChatGPT针对PCIe PHY IP 设计难点的高度概括的回答看着确实挺有道理的,可是对于严谨的(爱抬杠的)工程师们就不是很买账了,在他们看来高速速率传输下产生的信道串扰是设计人员遇到最具挑战性的问题,如何均衡信道远不是一句考虑数字信号完整性可以概括的,他们实际遇到的挑战和问题就不一一列举了,还是让他们和ChatGPT对刚吧。

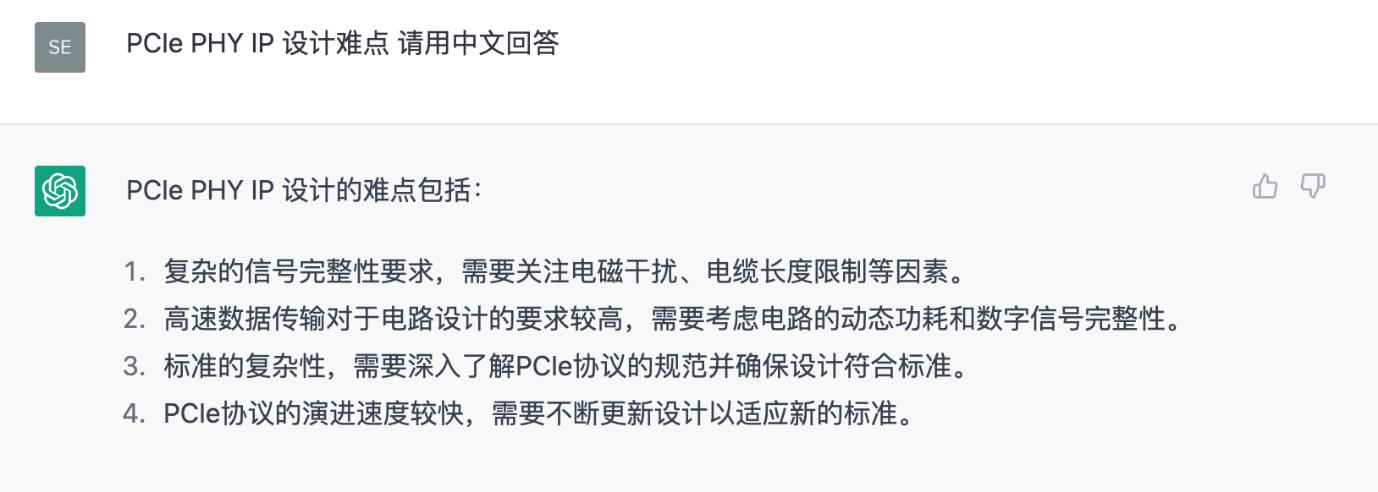

当问题进一步深入,工程师们可能终于抓到了ChatGPT的失误,针对PHY架构组成的第三点提出了反对意见,从PCIe总线的三种错误报告方式来看,分别是

1.Completions:通过Completion中的状态位向Request返回错误信息;

2.Poisoned Packet(又称为错误传递,Error告知接收端当前TLP的DataForwarding)Payload已经被破坏;

3.Error Message(错误消息):向主机报告错误信息。从错误报告的描述看,错误检测和恢复应该是由Controller来完成。

ChatGPT目前的知识储备帮着科普的能力还是有的,但对我们这些垂直技术领域还是了解的不够深,可能数据也不够多吧。希望奎芯自己的PCIe IP能尽快赋能更多人工智能芯片企业,为AI在人类生活各个领域的应用打好扎实的基础设施建设。

在2022年8月,奎芯PCIe 4.0 PHY已成功验证并正式发布。奎芯PCIe 4.0 PHY符合 PCI Express (PCIe®) 4.0、3.1、2.1、1.1 和 PIPE 4.4.1 规范,IP 尺寸仅为1.68mm,支持 x1、x2、x4等多种通道配置,并且支持通道拆分(1x4 或 2x2),在典型工况下功耗仅为450mW,并拥有强大的 BIST 功能来支撑量产测试。奎芯PCIe 4.0的发布标志着自主IP研发在T12nm工艺上的成功,也意味着奎芯科技在半导体IP事业更进一步。