存储架构升级下的高速接口演进路线

在“AI 驱动一切”的时代,数据爆发式增长正在重塑整个计算体系,而存储系统正成为支撑这一巨变的关键“中场”。根据 market.us 数据,全球存储芯片市场将在未来十年持续扩张,从 2024 年的 1251 亿美元跃升至 2034 年的 3920 亿美元,复合增长率达 12.1%,其中 DRAM 与 NAND Flash 占比合计超过 95%。

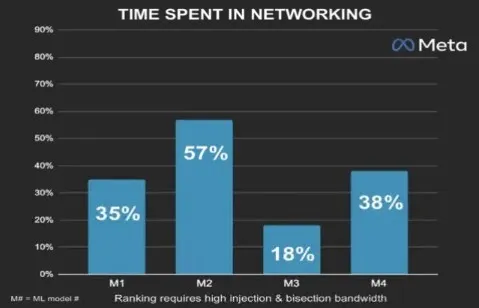

AI 的崛起正加速这一趋势,IDC 数据显示:2024 年全球企业在人工智能存储领域的支出达到 67 亿美元,预计 2025 年增至 76 亿美元,2028 年有望突破 102 亿美元,2023–2028 年复合增长率为 12.2%。这些应用对存储系统的挑战,远不止容量,更集中于读写带宽、访问延迟、接口效率和功耗优化等架构级指标。而连接 NAND 与控制器之间的接口,正在成为决定系统性能表现的关键路径。

ONFI(Open NAND Flash Interface)作为当前最广泛的 NAND 接口标准,自 2006 年发布以来已完成五次主要迭代,正在从 3600MT/s 向 4800MT/s+ 的速率 档位跃升,成为新一轮架构革新的核心触发点。本文将以 ONFI 5.1 及其未来演进为切入口,系统梳理 NAND 接口的技术路线、演进逻辑与产业趋势,提出 2025–2028 年间存储接口的四大关键演化方向。

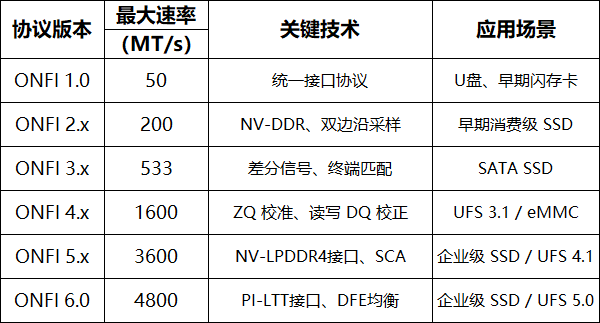

ONFI 协议演进概览:性能飞跃的逻辑主线

2025 年,ONFI 协议在保持物理层兼容性的基础上,持续迭代 PHY架构与时序机制,整体呈现三大趋势:

速率突破:主流接口速率突破3600MT/s,向4800MT/s迈进,满足AI训练存储带宽需求

架构优化:SCA 技术进入实用阶段,实现命令通道与数据通道物理分离,提升指令并发度。

高速传输保障技术:在≥4800MT/s场景中,PI-LTT+DFE成为必需:

PI-LTT(Power Isolated Low Tapped Termination) 解决信号衰减:动态低摆幅降低传输能耗

DFE(Decision Feedback Equalizer) 抑制码间干扰:确保BER<10⁻⁹(对比前代10⁻⁴)

总线速率与架构协同:突破性能瓶颈的核心逻辑

1. 速率演进:从3600到6400MT/s 的通道升级

随着 Page Size 从 4KB 向 16KB 扩展,单次数据传输量快速增长,接口带宽成为限制存储系统性能的关键因素。以 4KB 数据为例,从 200MT/s 升至3600MT/s,传输时延由 40us 降低至约 1.1us,等效提速超过 18 倍。

调研数据显示,2026年主流速率将向4800MT/s演进,ONFI 6.0方案渗透率预计达25%;5600MT/s和6400MT/s需至2027年之后逐步落地。

这一趋势将依赖以下三大核心技术:

信号完整性优化: DFE(ONFI 6.0标配)抑制码间干扰,提升信号完整性;

能效优化:Pi-LTT接口采用了更低摆幅信号协议,大幅降低高速数据传输功耗;

PHY 与控制器的Chiplet 异构集成,实现近距离、高密度互联,减少信号延迟路径。

2. 架构革新:SCA 技术崛起,重构命令传输路径

在高速 NAND 传输中,传统的命令与数据“时分复用”总线架构已逐渐成为瓶颈。尤其在速率超过 3600 MT/s 的场景中,总线利用率骤降至 50% 以下,严重制约整体吞吐性能。

SCA(Separate Command Address)架构提出将命令/地址与数据分离,通过独立通道并行传输,实现 100% 数据总线利用率。据 IP Nest 数据显示,具备 SCA 架构支持的 SSD 控制器,其小文件读写性能平均提升 45%,在 4KB 随机访问场景下,延迟从 80us 降至 45us,接近 DRAM 级响应体验。

截至 2025 年,SCA架构仍处于企业级试点阶段,预计2026年随ONFI 6.0控制器普及,成为高性能 NAND 的必备特征。

3. 能效优化:高速传输不等于高功耗

高速接口的另一大挑战来自能耗控制。在服务器、车载、边缘AI等高密度部署场景中,功耗始终是系统设计的重要考量。

传统LTT技术通过降低信号摆幅在≤3600MT/s场景实现显著节能;但当速率突破4800MT/s时,其固定阻抗特性引发信号反射,导致能效比急剧恶化。

ONFI 6.0引入的PI-LTT技术(含动态摆幅调节与阻抗自适应能力)通过以下机制抑制反射损耗:

动态摆幅调节:优化信号电压幅度

阻抗自适应:实时匹配信道阻抗特性

结合DFE均衡器消除码间干扰,该方案在4800MT/s速率下可实现:

系统级功耗降幅30-50%*

误码率降至10⁻⁹以下

2025–2028 年,能效比将成为衡量接口优劣的“隐形KPI”,高速 + 低功耗协同设计将成为主控与IP厂商的共识方向。

4. 生态协同:标准融合加速模块化部署

除了技术本体的进步,ONFI 协议的未来演进也正在与其他标准形成协同共振。

以 Chiplet 互连为例,ONFI 与 UCIe 协议的融合有望推动存储子系统实现 IP 级别的模块化部署,简化 SoC 设计流程,降低系统复杂度与验证成本。

ONFI 是基础,更是通向高性能存储的“高速公路”

ONFI 的演进不仅关乎速率突破,更体现出行业在架构设计、功耗控制和生态协同上的系统化思考。在 3600MT/s 成为“常态”的当下,6400MT/s+ 时代的挑战已不止于“快”,更在于“稳”和“省”。

未来3年,高速接口将成为承载 AI 服务器、边缘设备、车载计算等系统“不可缺失”的“运力基础”。而在这一演进过程中,具备深度协议理解与 IP 设计能力的厂商,将在标准推进、生态引导中扮演更关键角色。