在2023年4月,我们分享了一篇关于Chiplet D2D接口技术的文章,重点介绍了Chiplet的历史以及为何在算力时代选择Chiplet技术等主题。文章通过这些话题引出了Chiplet的关键技术之一,即D2D互联技术。在讨论D2D互联时,我们不可避免地要提到2023年度备受关注的UCIe互联协议。

作为全球UCIe互联的主要贡献者,英特尔在2023年9月的创新大会上展示了一款名为Pike Creek的测试芯片,该芯片由基于UCIe互联的小芯片构成,整合了包含英特尔3nm UCIe IP的芯片和包含台积电N3E Synopsys UCIe IP的芯片,通过英特尔EMIB封装实现通信。这款芯片成为全球首款基于不同公司、代工厂以及技术节点设计的UCIe互连芯片,备受瞩目。

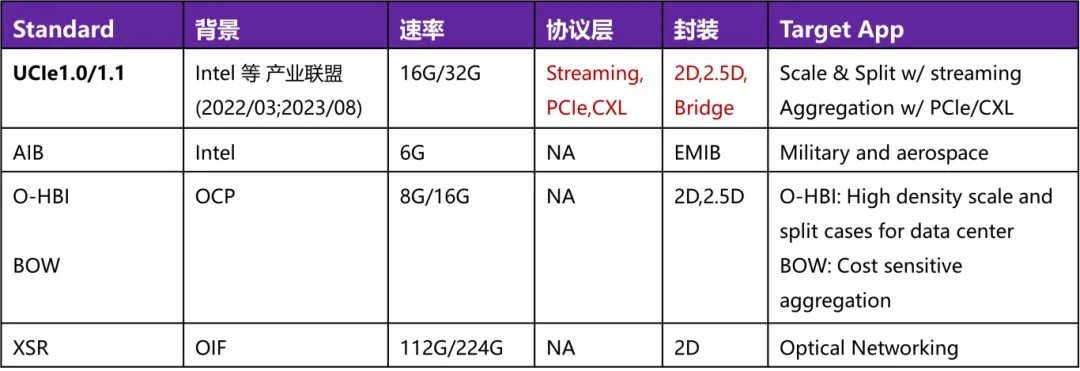

D2D接口协议对比

UCIe并非唯一的D2D接口协议。在UCIe协议出现之前,全球主要芯片企业,如英特尔、英伟达和AMD等,采用私有协议作为D2D互联协议。当时,超大型芯片公司并没有采用其他公司的芯片互联来扩展芯片能力的需求场景。直到英特尔基于AIB协议的技术积累,提出了跨公司、跨工艺互联的UCIe协议。

从上图可以看出,英特尔的AIB协议主要应用在军工和航空航天产品上。而基于AIB经验积累开发的UCIe协议,在速率、协议层的支持以及封装技术上都具有明显的优势。相比之下,类似HBI、BOW等协议自UCIe协议问世以来,更新频率逐渐降低,其规范的内容细致程度也远不及UCIe协议。

值得一提的是,中国全自主可控的Chiplet高速串口标准ACC 1.0于2023年3月20日发布。随后,中国Chiplet产业联盟还发布了ACC_RV 1.0车规级芯粒互联接口标准,为中国Chiplet互联技术的发展起到了关键的推动作用。

UCIe协议构成

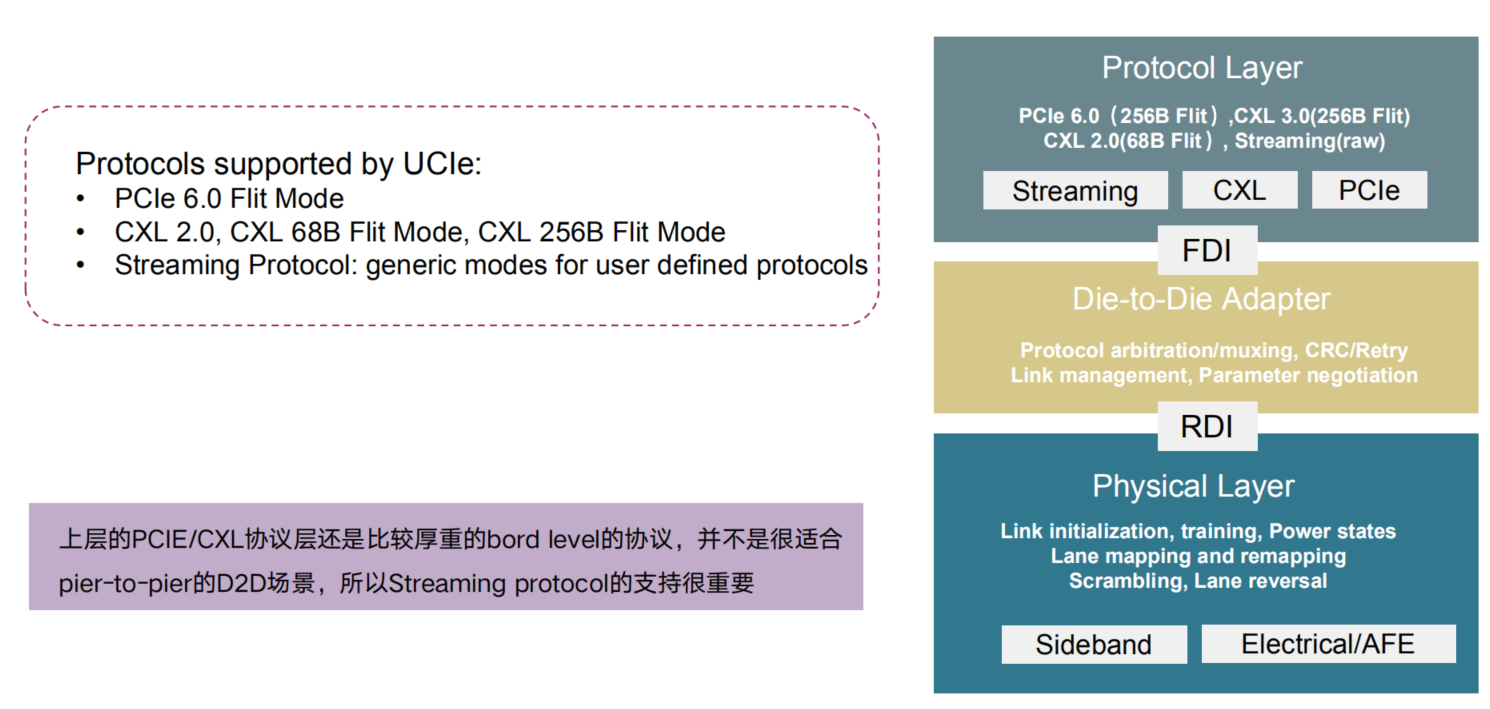

UCIe协议包含三个层级,分别是协议层(Protocol Layer)、适配层(Die-to-Die Adapter Layer)以及物理层(Physical Layer)。这三个层级在协议的整体结构中担任不同的角色,具体如下:

协议层(Protocol Layer):

UCIe支持的协议包括PCI Express、CXL和Streaming。

采用基于Flit的协议,以提供最高效率和减少延迟。

适配层(Die-to-Die Adapter Layer):

负责链路管理功能,包括协议仲裁和协商。

提供基于CRC和Retry的可选纠错功能。

物理层(Physical Layer):

包含Electrical/AFE和逻辑PHY,用于实现链路初始化、训练和校准算法,以及测试和修复功能。

边带(Sideband)用于实现两个芯片之间的参数交换和协商。

在协议层到适配层的接口被称为FDI(Flit Data Interface),而适配层到物理层的接口则称为RDI(Raw Data Interface)。在FDI的边界上,它具备同时支持多个协议层挂载的能力。在不同的应用场景下,可以选择使用不同的协议,而由适配层负责进行仲裁。这种应用在未来CXL中将变得非常重要。因为CXL本身涵盖三种协议:.io、.memory、.cache。这种设计允许在接入UCIe时实现无缝衔接,并直接通过一个通路传输。而在RDI的边界上,可以连接单一模块的PHY,也可以连接多个模块的PHY,这种配置非常灵活。因此,总体上说,整个多层边界的定义非常清晰。

目前,UCIe支持的都是Flit模式的传输(即固定包层的传输)。传输包的大小要么是68字节的Flit,要么是256字节的Flit,这取决于所采用的协议。例如,PCIe 6.0和CXL 3.0都采用256字节的Flit,而对于CXL 2.0,则需要转换成68字节的Flit模式进行传输。Streaming模式是兼容其他协议的一种模式,其要求是采用64字节的原始模式。其他协议或PCIe、CXL的其他版本可能需要进行转换,以适应这种原始模式进行传输。

作为UCIe产业联盟和中国计算机互连技术联盟(CCITA)的成员,奎芯科技致力于推动芯粒互联技术的发展和应用。在高速接口IP领域,奎芯科技拥有深厚的技术积累和丰富的产品系列。基于这些尖端的高速接口IP,奎芯科技提出了一种名为M2LINK的计算体系互联架构方案。

M2LINK包含三种Chiplet方案:C2IO,与串型总线接口相联;C2M,与内存总线相连;以及C2C,实现计算Die之间的互联。奎芯科技将不断努力以满足Chiplet领域芯片设计企业的需求,并致力于打造一个开放生态的Chiplet服务平台,为集成芯片和芯粒行业的创新和发展提供全方位的支持。