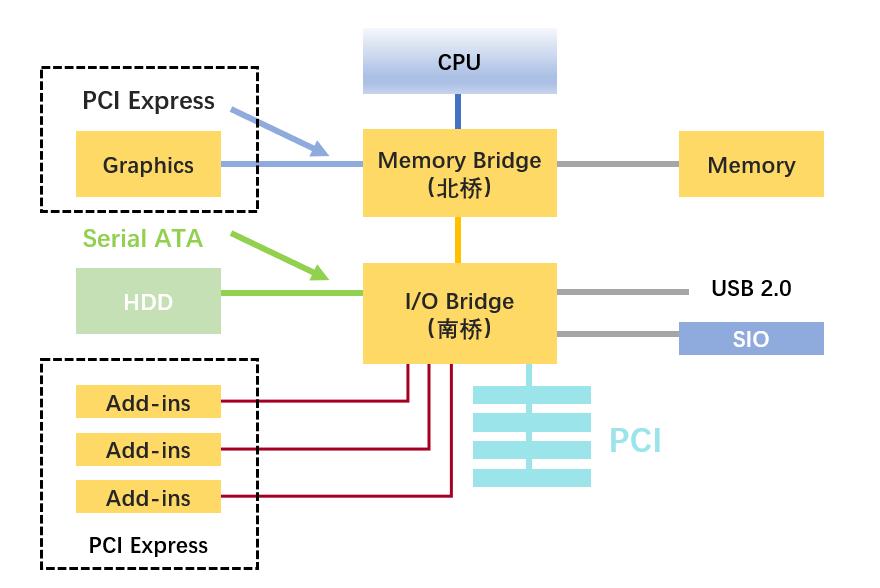

PCI Express (peripheral component interconnect express)是一种高速串行计算机扩展总线标准,简称PCI-E(以下简称PCIe),是计算机总线PCI的一种,它沿用现有的PCI编程概念及通讯标准,来建立更快的串行通信系统。1980 年,ISA(Industry Standard Architecture) 总线是第一个支持多种 I/O 适配卡的并列接口,可供绘图、音效、以及其它人机接口使用。PCI 的发展历经了几个革命性的阶段。为提高北桥与南桥的传输能力,Intel公司于2001年提出了将整个架构改为串行式Serdes的想法,让 PCI总线的架构被 PCIe所取代,扮演南北桥与芯片组间的连接。PCIe更可用于连接GPU和SSD固态硬盘,为高速运算和大型数据传输的主要接口,

如图1所示。

图1:PCIe为大型数据传输的主要接口

PCIe传输端口依传输数据量的需求不同,分为x1/x4/x8/x16/x32,x1主要用于音讯及网卡,x4/x8主要用于SSD固态硬盘,x16用于GPU,x32则较为少见。因为PCIe可实现高速大带宽传输,已逐渐侵蚀原先用于SSD传输接口的SATA、SAS之市场。根据调研机构IndustryARC预估,随着大型数据中心及服务器需求成长,PCIe市场2021-2026年CAGR(复合年均增长率)为20.6%,到2026年达到484.3亿美元。

图2:PICe 4 x4 应用于高速SSD固态硬盘

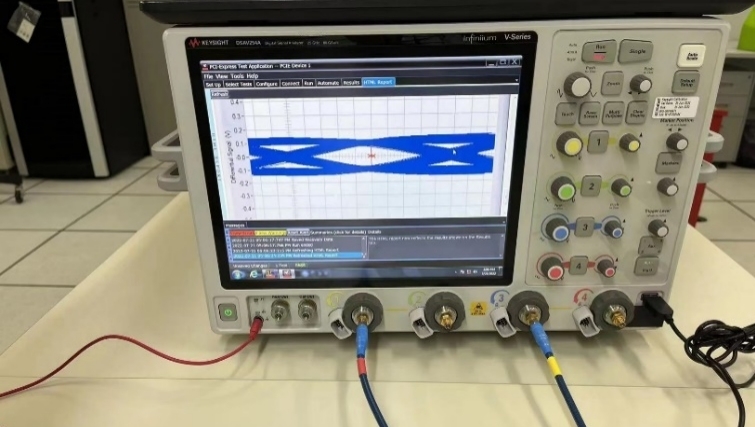

奎芯科技于今年流片成功并通过协议一致性测试的PCIe 4.0,符合 PCI Express (PCIe®) 4.0、3.1、2.1、1.1 和 PIPE 4.4.1 规范,IP 尺寸仅有1.68mm2 ,支持 x1、x2、x4的通道配置,并且支持通道拆分(1x4或2x2),在典型工况下功耗仅为450mW。目前已经进入了广泛的量产和应用阶段,同时PCIe 5.0等更先进制程的IP也在研发中。

图3:TX信号眼图生成

奎芯身为PCI-SIG协会的一员,已经成功在一些知名厂商的12纳米以上工艺节点得到验证并实现量产。公司目前已成功开发基于14个晶圆代工厂的横跨12nm到180nm制程的基础库IP超过230个,以及基于6个晶圆代工厂 横跨7nm到110nm的接口类IP超过180个。PCIe作为主板级互连、无源背板互连以及作为附加板的扩展卡接口,主要面向高性能计算、数据中心、人工智能、汽车电子、物联网等领域。奎芯科技在此众多高精尖领域都能提供市场急需的IP组合且有丰富成功案例,致力于开发先进制程的高性能半导体IP,期待与半导体领域的同仁们一起推动全球芯片制造向更先进技术的发展。