2024年11月5日至6日,国际集成电路展览会暨研讨会(IIC Shenzhen 2024)在深圳福田会展中心成功举办,奎芯科技以其业界领先的IP/Chiplet平台在Design Con专区吸引了众多目光。同期,联合创始人兼副总裁王晓阳在IP与IC设计论坛发表了《构建业界领先IP/Chiplet平台,推动AI和Chiplet技术创新》的主题演讲。

作为国内领先的半导体IP和Chiplet设计服务提供商,奎芯科技一直致力于通过技术创新推动行业发展。此次展会上,奎芯科技展示了其在UCIe接口技术领域的研发成果,这些成果正推动着生成式AI与高性能计算(HPC)应用的革命性突破。王晓阳先生在演讲中详细阐述了UCIe接口的性能特点,包括其高带宽、低延迟和卓越的兼容性。特别值得一提的是,奎芯科技的UCIe解决方案在连续七天的严格测试中,以零误码率的优异表现,充分证明了其稳定性和可靠性。此外,该接口IP在抗干扰能力和高低温环境下的出色表现,确保了在各种应用场景下的稳定运行。

在消费类应用领域,奎芯科技的UCIe解决方案展现出了广泛的应用潜力。通过灵活的NAND通道扩展,奎芯科技帮助客户实现了产品设计的优化,不仅降低了成本,还显著提升了性能。这一方案已成功应用于多款量产产品,赢得了市场的高度认可。

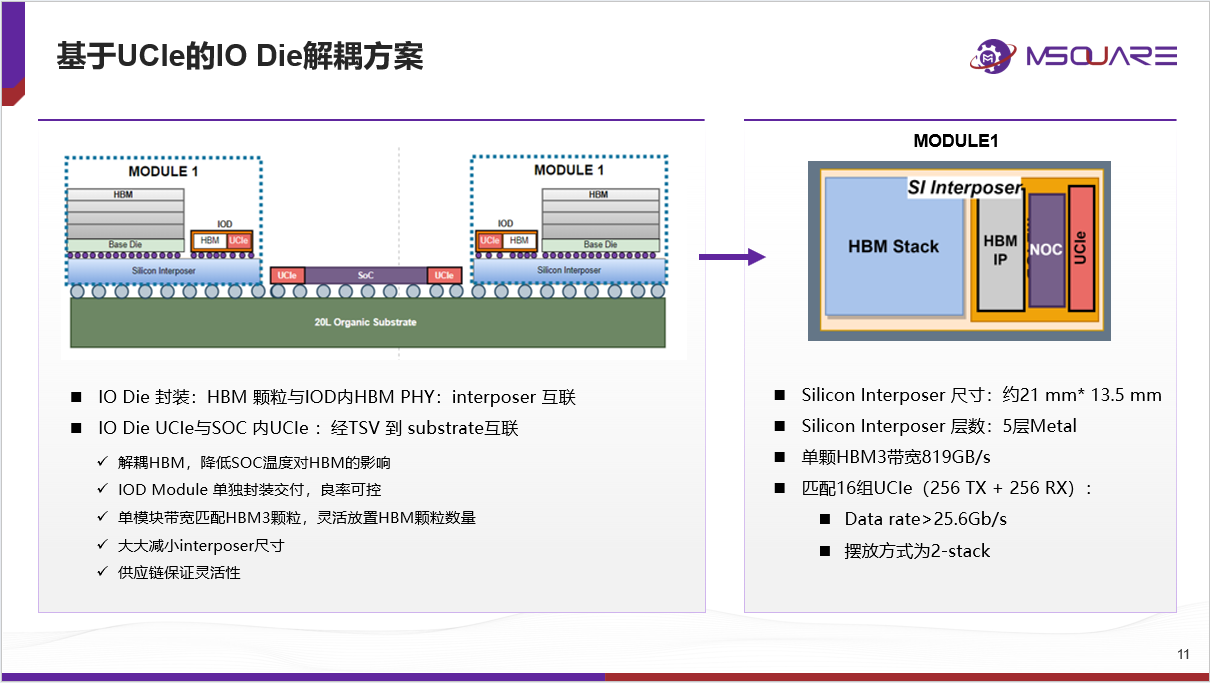

在高性能计算(HPC)领域,奎芯科技的UCIe IP更是大放异彩。奎芯科技基于12nm工艺的IO Die,单个HBM3接口带宽高达819.2GB/s,通过集成16个标准UCIe模块,系统单向传输速率可达惊人的8,192Gbps。这一突破性的性能表现,为HPC和AI数据中心应用提供了前所未有的IO支持,满足了高性能计算对数据传输速度和带宽的极高要求。

此外,奎芯科技展示了基于UCIe的IO Die解耦方案,其中IO Die封装包括HBM颗粒与IO Die内HBM PHY的互联,以及通过TSV(硅通孔)到基板的UCIe互连架构,实现了IO Die与SoC之间的高速传输。这种设计不仅提高了数据传输效率,还降低了功耗,为AI数据中心系统的海量数据在异构和同构die之间的高效传输提供了强有力的支持。

展望未来,奎芯科技将继续深化其在IP与Chiplet技术领域的研发,致力于扩展IP和Chiplet生态。奎芯科技将加强与上下游合作伙伴的紧密合作,共同推动UCIe、HBM、LPDDR等自研产品的广泛应用,为市场提供更加灵活、高效的解决方案。通过持续的技术创新和优质的产品服务,奎芯科技将继续引领AI领域的发展潮流,为全球半导体产业的繁荣贡献力量。