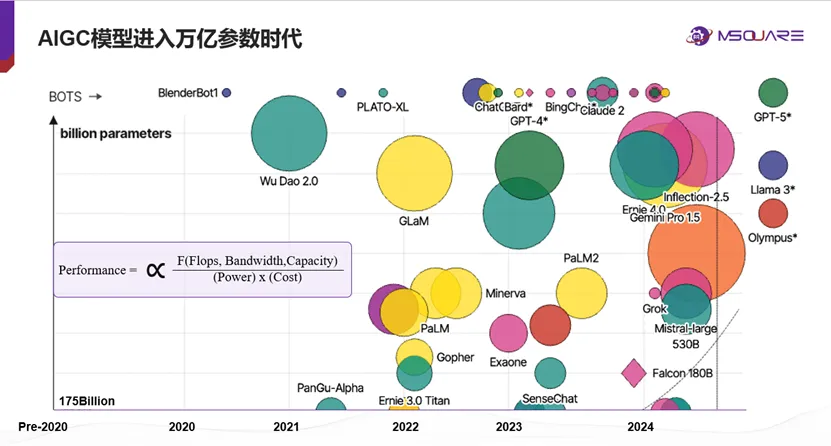

随着生成式AI和高性能计算(HPC)的加速发展,芯片互联技术正在经历一场革命。面对越来越复杂的应用场景,对芯片间接口的带宽、延迟和功耗提出了前所未有的挑战。作为国产芯片互联技术的探索者,奎芯科技凭借自主研发的UCIe接口解决方案,为行业带来了更高效、更稳定的芯片间互联支持。

生成式AI和HPC应用对数据处理提出了极高要求:从超大规模模型的训练到复杂推理任务的部署,对芯片间接口的带宽需求不断增加。传统互联方案在面对这些挑战时显得力不从心,例如:

高吞吐量数据传输受限,无法满足AI任务对实时响应的需求。

数据中心对功耗和可靠性的严格要求,推动行业寻找更高效的解决方案。

UCIe接口作为新一代互联标准,通过低延迟、高带宽的技术优势,正在成为解决这一挑战的关键。

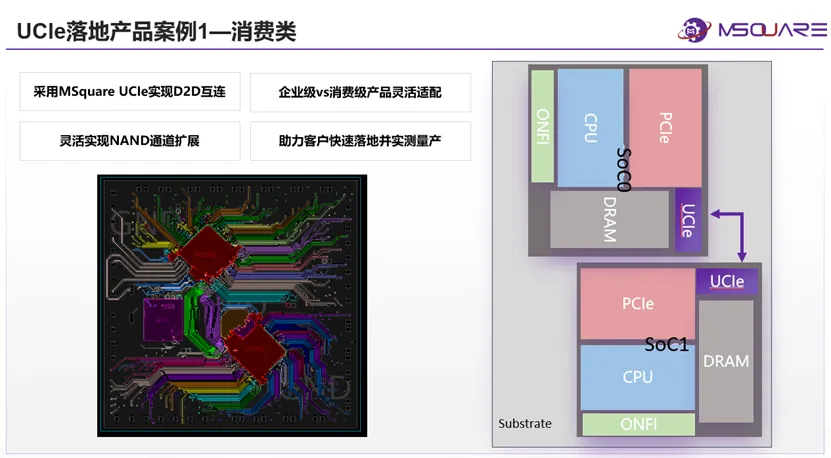

在消费类电子产品中,性能优化与成本控制一直是一对矛盾体。奎芯科技的UCIe接口IP通过灵活的NAND通道扩展,帮助客户大幅提升数据吞吐能力的同时,又显著降低了设计成本。

例如,在某消费级存储产品中,通过UCIe技术实现了模块化设计,不仅提升了产品性能,还缩短了上市时间。测试结果显示,其数据传输效率较传统方案提升了35%,并显著降低了功耗,产品的快速上市帮助客户在竞争激烈的市场中抢占先机。

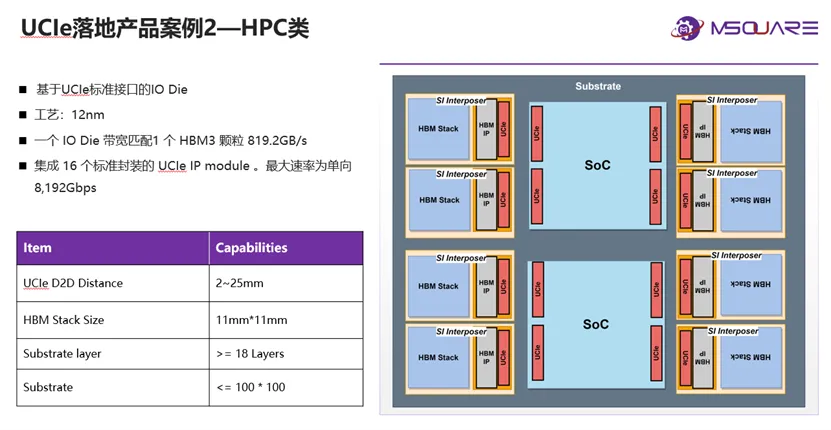

在高性能计算领域,奎芯科技基于12nm工艺的UCIe IO Die解决方案,通过集成16个标准UCIe模块,实现了单向8,192Gbps的超高带宽,为生成式AI的海量数据处理需求提供了坚实的技术支撑。

尤其在数据中心中,该方案通过TSV互联架构,将HBM颗粒与SoC的连接效率提升了20%以上,同时降低了系统功耗。这种设计大幅减少了封装面积,并优化了冷却需求,为AI模型的高效训练创造了理想条件。

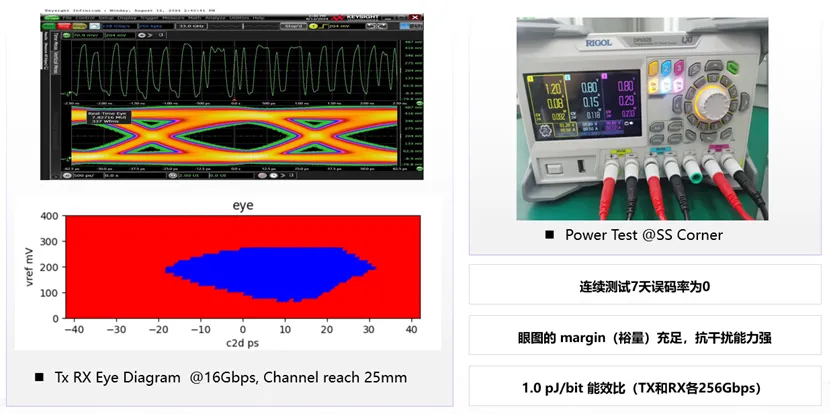

奎芯科技的UCIe解决方案不仅在性能上实现了突破,更在可靠性和稳定性方面展现了卓越表现:

通过严格高低温环境测试,展现卓越的抗干扰能力与稳定性。

以1.0pJ/bit的能效比实现高带宽传输,降低数据中心能耗。

支持多种接口协议(如PCIe、AXI等),满足不同场景需求。

UCIe技术的不断发展,正推动芯片间接口从传统的2D互联迈向更先进的3D封装。作为UCIe技术领域的深耕者,奎芯科技将继续致力于技术创新,为生成式AI和HPC等高性能计算场景提供更加优质的解决方案。从消费级到企业级,从卓越的性能到稳定的可靠性,奎芯科技的UCIe解决方案正在重新定义芯片互联的未来,为行业注入源源不断的新动能。