随着深度学习、大模型和AI应用的快速发展,数据中心对计算能力的需求呈指数级增长。传统的CPU-GPU架构在带宽、延迟和能效方面逐渐暴露出瓶颈,尤其是内存带宽的限制,已成为制约AI训练和实时分析等关键任务的主要障碍。

存储与运算之间的性能鸿沟:

因处理器与存储器工艺、封装、需求差异,二者性能差距持续扩大:存储器访问速度落后于处理器的数据处理需求,形成数据交换通路狭窄及高能耗问题;因此,在算力需求爆发式增长的数字化时代,存储与运算之间形成前所未有的鸿沟。

传统的GDDR和DDR内存的带宽限制,已成为制约AI训练、实时分析等关键业务发展的主要障碍。

HBM3内存通过3D堆叠技术实现1024位总线宽度,堆叠层数突破12层,配合TSV硅通孔技术实现6.4Gbps/pin的传输速率。在能效表现上,其功耗效率达到<0.6pJ/bit,较传统DDR5内存提升2-3倍以上。这些技术特性使HBM3具备819GB/s的极致带宽,完美匹配新一代GPU和AI加速器的数据处理需求。

与此同时,芯片间互连技术需突破物理限制,UCIe(Universal Chiplet Interconnect Express)通过标准化Die间互连协议,为多芯片异构集成提供了高达32 Gbps/Pin的传输速率和低延迟通信能力。

HBM3通过TSV(硅通孔)垂直堆叠与逻辑芯片封装,而UCIe则作为Die间高速互连的关键桥梁。这种架构可显著提升数据中心服务器的能效比(PUE),同时支持大规模定制化设计需求。UCIe的Die级互连减少PCB板级信号损耗,较传统SerDes方案降低30%功耗;HBM3的带宽密度减少内存占板面积,综合PUE可优化至1.1以下。

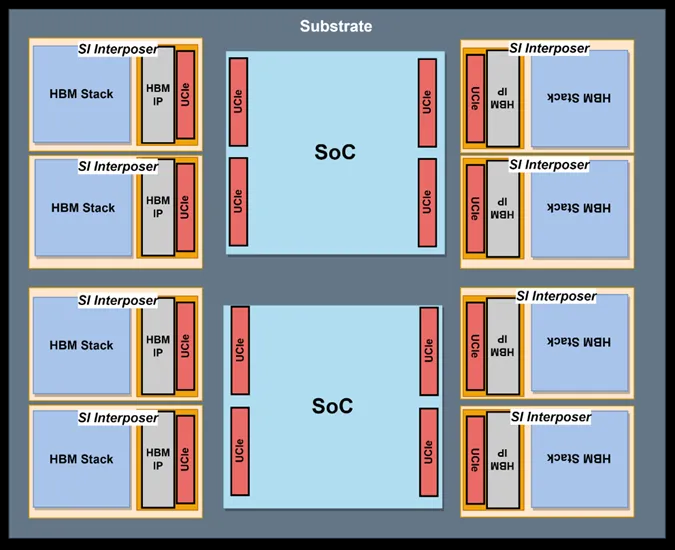

奎芯科技(MSquare Technology)基于HBM3和UCIe融合的Chiplet产品落地方案如下:

1)HBM3的高容量(16GB/颗)可存储千亿参数模型权重,避免数据在不同存储层级间频繁调度,提高训练效率。

2)UCIe的多Die互连能力允许GPU集群动态扩展算力,缩短训练周期。

UCIe的低延迟特性(<10ns)结合HBM3带宽,可支持边缘数据中心对视频流、传感器数据的实时分析。

基于UCIe与HBM3的协同IO Die架构为数据中心提供了高带宽、低延迟、高能效的解决方案,为未来的数据中心提供强劲支撑。然而,规模化部署仍面临挑战,例如标准化、散热管理以及成本优化问题。

随着UCIe联盟推动互连协议统一及封装技术成熟,该架构有望在2025-2030年成为超大规模数据中心的主流方案,支撑下一代AI、元宇宙等应用场景。

这一变革性的架构,正在重塑数据中心的未来!